Pipeline

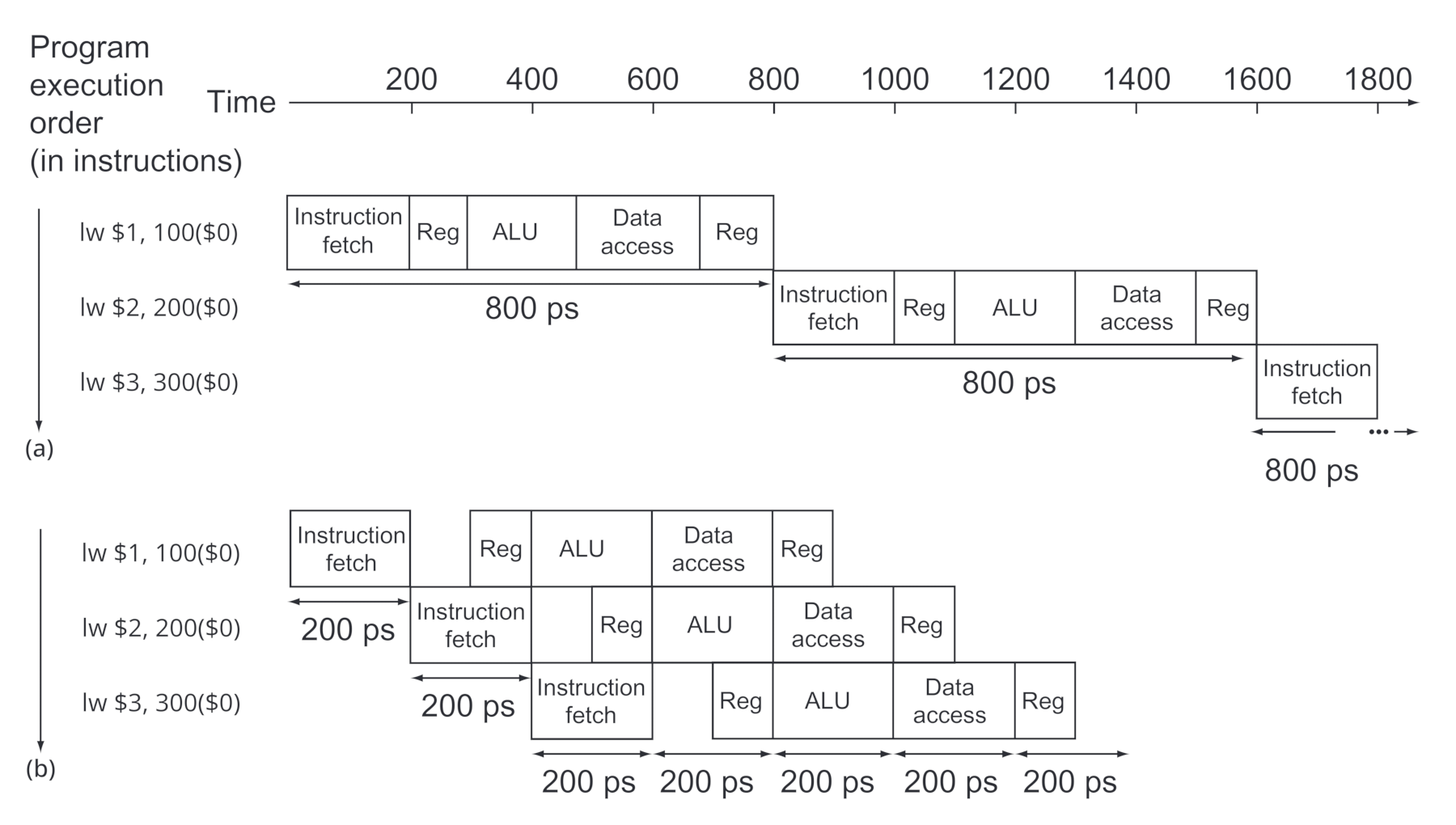

Ogni ciclo della CPU a singolo ciclo può essere suddiviso in unità funzionali, cioè delle operazioni fondamentali che possono essere parallelizzate per ottenere la CPU pipeline:

- IF (Instruction Fetch): lettura dell'istruzione e incremento PC

- ID (Instruction Decode): scomposizione istruzione (i 32 bit) e lettura registri

- EX (Execute): esecuzione ALU (per

add/lw/sw) e calcolo indirizzo perbeq - MEM (Memory Access): lettura/scrittura in memoria (per

lw/sw) - WB (Write Back): scrittura sul registro (per

add/lw)

L'implementazione avviene eseguendo ogni unità funzionale parallelamente alle istruzioni successive.